## МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ имени Н.Э. БАУМАНА

## Учебное пособие

Методические указания по выполнению домашних заданий по единому комплексному заданию по блоку дисциплины

«Системотехника ЭВС, комплексы и сети»

МГТУ имени Н.Э. Баумана

# МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ имени Н.Э. БАУМАНА

Методические указания по выполнению домашних заданий по единому комплексному заданию по блоку дисциплины

«Системотехника ЭВС, комплексы и сети»

Москва МГТУ имени Н.Э. Баумана

2012

УДК 681.3.06(075.8) ББК 32.973-018 И201

Методические указания по выполнению домашних заданий по единому комплексному заданию по блоку дисциплины «Системотехника ЭВС, комплексы и сети» / Коллектив авторов — М.: МГТУ им. Н.Э. Баумана, 2012. — 13 с.: ил.

В методических указаниях рассмотрены основные этапы, их последовательность и содержание по выполнению домашних заданий курсовой работы по единому комплексному заданию по блоку дисциплины «Системотехника ЭВС, комплексы и сети».

Ил. 39. Табл. 5. Библиогр. 7 назв.

УДК 681.3.06(075.8)

## СОДЕРЖАНИЕ

| 1 РАЗРАБОТКА МОДУЛЯ КОНТРОЛЕРА VGA  | 4  |

|-------------------------------------|----|

| Выводы                              |    |

| 2 МОДЕЛИРОВАНИЕ РАЗРАБОТАННОЙ СХЕМЫ |    |

|                                     |    |

| 2.1 Входные данные                  |    |

| 2.2 Результаты моделирования        | 9  |

| Выводы                              | 11 |

| ЗАКЛЮЧЕНИЕ                          | 12 |

| СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ    | 13 |

### 1 РАЗРАБОТКА МОДУЛЯ КОНТРОЛЕРА VGA.

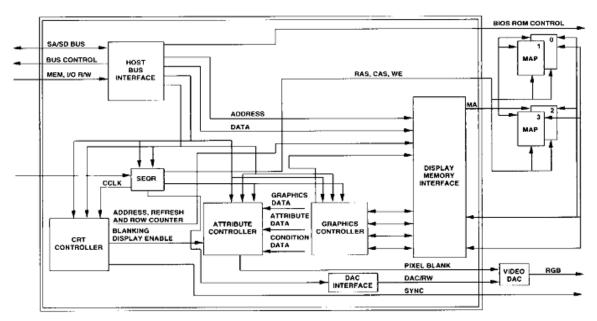

На основании исследований, проведённых в прошлых ДЗ, была разработана структурная схема контролера VGA, представленная на рисунке 1.

Контролер включает 7 основных компонентов: контроллер последовательности, CRT контроллер, графический контроллер, контроллер атрибутов, поддержка ЦАП логики, интерфейс системной шины и интерфейс отображения шины памяти. Эти компоненты используются для генерации выходного видео и синхронизации видео памяти и монитора.

Рисунок 1 - Функциональная схема контролера VGA

Видеоадаптеры VGA имеют большое количество регистров.. Большая часть регистров VGA доступна только для записи, что создает определенные проблемы, особенно для мультизадачных систем.

Некоторые фирмы-изготовители видеоадаптеров выпускают платы видеоадаптеров совместимые с VGA, для регистров которых разрешена также и операция чтения. В адаптерах VGA практически все регистры доступны как для записи, так и для чтения.

Доступ к большинству регистров видеоадаптеров осуществляется в два этапа: через один порт ввода/вывода выбирается номер интересующего вас регистра, а затем через другой порт ввода/вывода осуществляется обмен данными. Такая организация регистров позволяет сэкономить большое количество портов центрального процессора. Остальные регистры адресуются непосредственно через соответствующие порты ввода/вывода - каждому регистру соответствует один порт ввода/вывода.

В данной работе моделирование работы контролера VGA выполнено на основе работы графического контролера

Графический контроллер осуществляет обмен данными между видеопамятью и процессором. Графический контроллер может выполнять над данными, поступающими в видеопамять, простейшие логические операции: И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, циклический сдвиг.

#### Исполнение видеоадаптером операции записи

При чтении процессором данных из видеопамяти они также запоминаются в регистрах-защелках, расположенных на плате видеоадаптера. Когда затем выполняется цикл записи, то над данными, находящимися в этих регистрах, и над данными, поступающими от процессора могут производится следующие логические операции:

- Запись неизмененных данных процессора в видеопамять.

- Циклический сдвиг записываемых данных процессора.

- Выполненеие булевой операции И между записываемыми данными и данными в регистрах-защелках.

- Выполненеие булевой операции ИЛИ между записываемыми данными и данными в регистрах-защелках.

- Выполненеие булевой операции ИСКЛЮЧАЮЩЕЕ ИЛИ между записываемыми данными и данными в регистрах-защелках.

Таким образом, видеоадаптер может выполнять часть работы по обработке видеоданных.

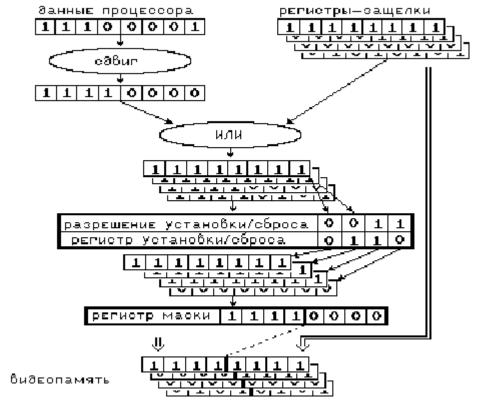

Рисунок 6.16 иллюстрирует выполнение графическим контроллером операции записи данных в видеопамять:

#### Рисунок 2 - Запись данных в видеопамять.

Байт, записываемый прцесоором в видеопамять (11100001b) поступает в графический контроллер. В соответствии со значением регистра циклического сдвига и выбора функции (регистры адаптеров описаны в следующем разделе), происходит циклический сдвиг на один бит содержимого записываемого в видеопамять байта. Затем результат складывается по логике ИЛИ с содержимым регистров-защелок. Какая булева функция используется - ИЛИ, И, ИСКЛЮЧАЮЩЕЕ ИЛИ также определяется регистром циклического сдвига и выбора функции.

Дальнейшие преобразования происходят в соответствии со значениями регистра разрешения установки/сброса и регистра установки/сброса:

- Если бит регистра разрешения установки/сброса, управляющий данным цветовым слоем равен нулю, то байт, записываемый в видеопамять не изменяется.

- Если бит регистра разрешения установки/сброса, управляющий данным цветовым слоем равен единице, то в него записывается байт, все биты которого устанавливаются в соответствии со значением регистра установки/сброса для данного цветового слоя.

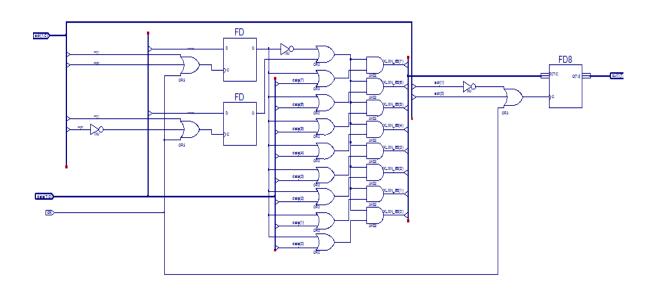

Логическая схема проекта построена на основе работы регистров разрешения установки/сброса и регистра установки/сброса.

Рисунок 3 – Схема логическая проекта

Где на рисунке 3 FD – одноразрядные регистры, соответственно регистр разрешения установки/сброса и регистр установки/сброса.

FDB – 8 разрядный регистр, выполняющий функцию видео памяти.

На вход схемы подаются 2х разрядная шина адреса adr, на которой происходит выбор регистра для записи, 8 разразрядная шина данных data, и тактовый сигнал clk.

Результатом проделанной работы является логическая схема, реализующая работу регистров графического контролера.

### Выводы

В ходе разработки контроле VGA был получен алгоритм его работы для реализации в Xilinx ISE Design Studio. Далее этот алгоритм был разбит на работу компонентов, и впоследствии собран упрощенный проект работы одного из компонентов с регистрами управления.

## 2 МОДЕЛИРОВАНИЕ РАЗРАБОТАННОЙ СХЕМЫ

Следующим этапом разработки логического проекта для ПЛИС является моделирование разработанной схемы. Для этого используется симулятор ISim, идущий в комплекте с Xilinx ISE Design Studio.

### 2.1 Входные данные

Чтобы проверить правильность работы графического контролера, на его вход необходимо подать некоторые данные и контролировать правильность их отображения на выходе. Для этого был разработан файл входных сигналов (Test Bench):

Исходный код файла тестовых сигналов представлен в листинге 4.

#### Листинг 1 –Verilog Test Fixture

```

// Verilog test fixture created from schematic C:\Program\X\dz4_3\dz.sch - Mon Jun 27 09:25:57 2011

`timescale 1ns / 1ps

module dz_dz_sch_tb();

// Inputs

reg [1:0] adr;

reg [7:0] data;

reg clk;

// Output

wire [7:0] out1;

// Bidirs

// Instantiate the UUT

dz UUT (

.adr(adr),

.data(data),

.clk(clk),

.out1(out1)

);

// Initialize Inputs

//`ifdef auto_initf

always begin

#10 \text{ clk} = \text{~clk};

end;

initial begin

clk = 0;

data = 8'b000000000;

adr = 2'b00;

#100 adr = 2'b01;

#100 adr = 2'b10;

```

```

data = 8'b10101010;

#100 adr = 2'b00;

#10 data = 8'b00000001;

#100 adr = 2'b10;

#100 adr = 2'b01;

data = 8'b00000000;

#100 adr = 2'b10;

#100 adr = 2'b10;

#100 adr = 2'b10;

#100 adr = 2'b10;

data = 8'b10000010;

#100 data = 8'b00101000;

end

```

## 2.2 Результаты моделирования

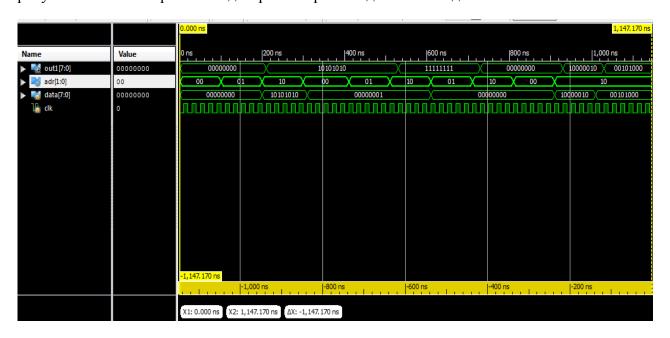

Далее данный файл был использован при моделировании логической схемы. На рисунке 4 показана временная диаграмма приёма одного байта данных.

Рисунок 4 – Результаты моделирования работы схемы

Где на рисунке 4:

- Out1[7:0] уровни логических сигналов на шине выхода;

- Adr[1:0] уровни логических сигналов на шине адреса;

- data[7:0] уровни логических сигналов на шине данных;

#### • clk- тактовый сигнал.

На шине данных происходит выбор регистра для записи данных. Так адрес 00 соответствует адресу регистра разрешения установки/сброса, 01 — адресу регистра установки/сброса, а 10 — регистру видео памяти.

Запись в регистры с адресами 00 и 01 осуществляется по 0-му разряду 8-ми разрядной шины данных data(7:0).

В момент времени от 0нс до 200нс происходит запись в регистры 00 и 01 значений 0. Так как в случае, когда на регистре 00(регистр разрешения установки/сброса) будет значение 0, данные на видео память будут поступать без изменения с шины данных, что и наблюдается по результатам моделирования, после выбора адреса видео памяти 10(момент времени от 200нс до 300нс). Так в регистр видео памяти записывается байт 10101010.

Далее в момент времени от 300нс до 500нс в регистры управления графическим контролером записываются 1(выбором адресов регистров и установкой на шине адреса значения 00000001). После чего на шине адреса выбирается адрес регистра видео памяти 10, в результате чего в регистр видео памяти записывается байт, состоящий из единиц, т.к. значения обоих регистров управления равно 1, что соответствует тому, что разрешена замена данных, которые заменяются на значения из регистра установки/сброса, значение которого равно 1.

После записи данных в регистр видео памяти на шине адреса в момент времени 600нс выставляется адрес регистра разрешения/сброса 10, а на шине данных байт 00000000, в результате чего в регистр записывается значение 0. Далее на шине адреса выбирается адрес регистра видео памяти 10 в момент времени 700нс, в результате чего в регистр видео памяти записывается байт состоящий из нулей.

В момент времени 800нс на шине адреса выставляется адрес регистра разрешения установки/сброса, а на шине данных установлен байт 00000000. В результате чего в данный регистр записывается число 0, что запрещает замену бит из шины данных, при записи в регистр видео памяти.

Далее в момент времени 900нс на шине данных выставляется адрес регистра видео памяти 10, а на шине данных байт 10000010, в результате чего в регистр видео памяти записывает байт 10000010. Аналогично в момент времени 1мкс в регистр видео памяти записывает байт 00101000.

## Выводы

С целью проведения моделирования проекта был разработан файл на языке verilog, описывающий входные сигналы. Анализ полученных результатов моделирования показал, что разработанная схема полностью выполняет заложенную в нее функцию, а именно преобразовывает последовательный входной сигнал в параллельный выходной.

## ЗАКЛЮЧЕНИЕ

В рамках данной работы была разработана схема работы графического контролера с регистрами разрешения установки/сброса, и регистром установки/сброса.

Правильность работы модуля была проверена посредством моделирования разработанной схемы в симуляторе ISim. Для этого был создан файл входных сигналов (Test Bench), и проведён анализ графиков, полученных в результате моделирования, по результатам которого был сделан вывод о правильности работы схемы.

## СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

- 1. Материалы сайта <a href="http://frolov-lib.ru/books/bsp/v03/ch5">http://frolov-lib.ru/books/bsp/v03/ch5</a> 2.htm.

- 2. Захаров Е.В., Юдаев А.С., Домашнее задание №2 по курсу «Системотехника ЭВС», 2010